Filter deballasting control of droop-controlled inverters

Ph.D. Student: Gurupraanesh Raman | Advisor: Jimmy C.-H. Peng | Project Duration: 2019-2021

Summary

Filter Deballasting Control (FDC) enhances stability in droop-controlled inverter microgrids during supervisory delays or failures. This summary outlines the core problem, proposed solution, and key results from the IEEE Transactions on Power Electronics paper [Read More].

Problem Statement

Droop-controlled inverters in islanded microgrids risk instability from topology changes, plug-and-play operations, or varying droop gains, as stability depends on global parameters like network impedances and inverter count. Supervisory controllers tune droop gains (e.g., kf, kv) via low-bandwidth links, but delays, communication failures, or cyberattacks compromise damping, potentially causing inverter tripping in milliseconds to seconds.

Figure 1. Control block diagram for conventional and FDC modes.

Proposed Solution

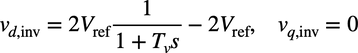

FDC activates a quasi-open-loop mode, deballasting the inverter's LC filter inductance (Lf) into the network to boost equivalent impedance and reduce active/reactive power cross-coupling, improving damping without hardware changes. A slow voltage recovery integrator (Tv ≫ Tc) ensures steady-state power sharing matches conventional mode:

A lead-lag power filter compensates line dynamics lag:

Small-signal models (order 5n for n inverters) use Kron-reduced Ybus to include filter effects, confirming expanded stability regions.

Figure 2. (a) Stability region for the single-inverter system under the conventional mode and expanded stability region under FDC mode. (b) Damping ratio of the single-inverter system under the FDC mode for different values of filter inductance Lf, with the droop gains fixed at (1%, 5%). When Lf = 0, the system has the same damping under the conventional mode.

Key Contributions

-

Decentralised fallback: Leverages filter as "stability ballast" for interim damping, robust to comms issues; smooth mode transitions preserve P/Q sharing.

-

Lead-lag enhancement: Eliminates kv limits from inductive dominance, guaranteeing stability across droop gains and R/X ratios.

-

Extensibility: Applies to generalised droop, virtual impedance; validated on 3-inverter lab setup (48V, 1kVA).

Figure 3. Experimental waveforms (for Phase A) demonstrating the proposed strategy for an inverter connected to an infinite bus. Experimental procedure–Before t1: Conventional mode with kf = 0.5%, t1: Load-2 switched ON, conventional mode with kf = 2.8%, t2: FDC activated, t3: Load-2 switched OFF, t4: Revert to conventional mode with kf = 0.5%, t5: Load-2 switched ON. Scale-5 s/div, 100 V/div, 5 A/div, 100 W/φ/div.

Validation Results

Eigenvalue analysis shows critical damping rising from 0.114 to 0.290; experiments confirm kf limit expands from 2.8 to 11 (at kv = 5). Multi-inverter tests verify equal sharing under resistive/inductive/capacitive loads and plug-and-play.

Figure 4. (a) Location of poles for the single-inverter system under the conventional (blue x) and FDC (red o) modes. (b) The zoomed version of the same plot showing only the low frequency poles. The damping of the critical pole-pair is higher under FDC.